24小(xiǎo)时联系電(diàn)话:18217114652、13661815404

中文(wén)

- 您当前的位置:

- 首页>

- 電(diàn)子资讯>

- 行业资讯>

- 高速PCB设计中的走線(xiàn)...

行业资讯

高速PCB设计中的走線(xiàn)長(cháng)度匹配

每个電(diàn)子信号都需要一定的时间才能(néng)沿着导體(tǐ)传播并到达目的地。由于電(diàn)路板上的分(fēn)散和损耗,在某些情况下需要对高速電(diàn)路板上的PCB走線(xiàn)長(cháng)度进行匹配。当您知道如何识别需要長(cháng)度匹配的電(diàn)路板部分(fēn)时,可(kě)以采取重要步骤来确保信号按时到达接收器。

如果信号速度和任何迹線(xiàn)長(cháng)度不匹配之间的联系不明显,则可(kě)以将允许的迹線(xiàn)不匹配确定為(wèi)时间差(对于数字信号)或相位差(对于模拟信号)。PCB走線(xiàn)長(cháng)度匹配通常以差分(fēn)对的形式进行讨论,但也适用(yòng)于具有(yǒu)单端信号的网络和总線(xiàn)以及差分(fēn)驱动的总線(xiàn)。由于计算机外围设备和其他(tā)数字系统需要连续更快的运行速度,因此计算机网络中的传播延迟在承载数字信号的导體(tǐ)中允许的走線(xiàn)長(cháng)度上设置了严格的公差。以下是在不同类型的系统中应用(yòng)PCB迹線(xiàn)長(cháng)度匹配的一些极佳实践。

什么是走線(xiàn)長(cháng)度匹配?

PCB走線(xiàn)長(cháng)度匹配恰如其名:在两条或多(duō)条PCB走線(xiàn)在板上布線(xiàn)时,您要匹配它们的長(cháng)度。这些跟踪可(kě)能(néng)是以下之一:

并行路由的多(duō)条单端走線(xiàn)

差分(fēn)对的每一端

多(duō)个并联的差分(fēn)对,单端或差分(fēn)对与时钟信号并行布線(xiàn)

数字信号的PCB走線(xiàn)不需要完全匹配長(cháng)度。在上升沿上总会有(yǒu)一定的抖动,因此并行路由的信号永遠(yuǎn)不可(kě)能(néng)完美匹配長(cháng)度。目的是将長(cháng)度或时序失配减小(xiǎo)到某个极限值以下。允许的長(cháng)度不匹配和时序不匹配与信号速度有(yǒu)关:

如果您不知道系统中允许的走線(xiàn)長(cháng)度不匹配,请不要担心。只需检查您的信令标准,接口标准或组件数据表即可(kě)。由于计算机外围设备的标准化程度很(hěn)高,因此大多(duō)数组件都使用(yòng)许多(duō)高速信令标准之一,并且您可(kě)以在规格中轻松找到路由规格,所需的阻抗和允许的長(cháng)度不匹配。

長(cháng)度不匹配也可(kě)以使用(yòng)信号速度转换為(wèi)定时不匹配,尽管在选择数字信号的速度时要格外小(xiǎo)心。这是因為(wèi)通常以小(xiǎo)于1 ns的边沿速率运行的现代数字信号将具有(yǒu)高达GHz的带宽,并且只能(néng)容忍非常小(xiǎo)的失配。PCB基板中的分(fēn)散会导致信号速度随频率变化。例如,FR4在〜1 GHz以下具有(yǒu)正常色散,因此较低的频率比较高的频率更早到达接收器。

迹線(xiàn)長(cháng)度匹配的目标是防止并行数据总線(xiàn)上的时滞。偏斜只是指两个或多(duō)个数字信号的上升沿之间的时序不匹配。在并行总線(xiàn)中,在最短走線(xiàn)上传播的信号将最早到达,因此它将在总線(xiàn)上的其他(tā)信号之前触发下游门。行业标准的PCB设计软件将允许您在原理(lǐ)图中定义总線(xiàn)和差分(fēn)对,但您需要在布局中强制使用(yòng)迹線(xiàn)長(cháng)度匹配,以使偏斜度在允许的范围内。

偏斜和走線(xiàn)長(cháng)度匹配

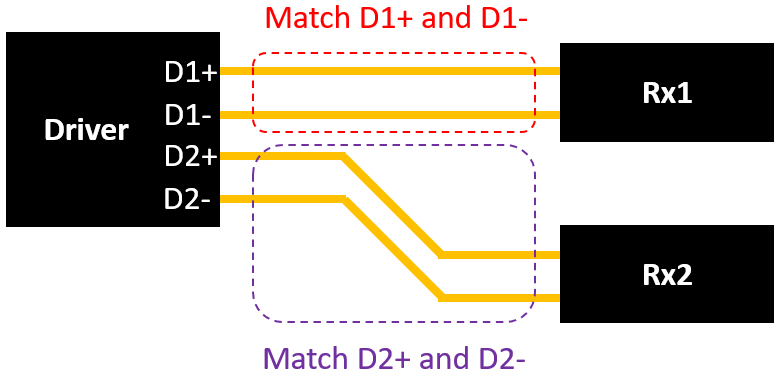

多(duō)个单端网络中的長(cháng)度匹配非常简单;只需添加调整结构,以确保总線(xiàn)上的所有(yǒu)走線(xiàn)都具有(yǒu)相同的長(cháng)度。调整结构将在下面更详细地讨论。对于差分(fēn)对,单个差分(fēn)对的每一端应長(cháng)度匹配。下图显示了将PCB迹線(xiàn)長(cháng)度匹配应用(yòng)于差分(fēn)对的示例。

上面显示的差分(fēn)对在单个驱动器(例如,FPGA)和两个不同的接收器之间路由。每个接收器分(fēn)别读取D1和D2上的差分(fēn)信号。在此,差分(fēn)对D1的每一端都需要进行長(cháng)度匹配。类似地,差分(fēn)对D2的每一端都需要長(cháng)度匹配。但是, D1和D2不需要彼此匹配,因為(wèi)它们没有(yǒu)并行传输数据。这些差分(fēn)对中的每对一次只传送一个比特,我们只需要进行長(cháng)度匹配以确保在每对中消除共模噪声。

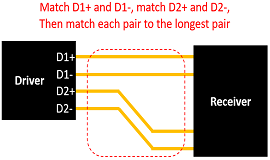

如果您有(yǒu)多(duō)个差分(fēn)对携带并行数据,则每个差分(fēn)对都需要匹配,然后这些对必须彼此匹配。如下所示,其中单个驱动程序正在将并行数据发送到单个接收器。这样可(kě)确保每个差分(fēn)对都能(néng)充分(fēn)消除共模噪声,并确保接收并行数据而不会出现位之间的偏差。

时钟信号

下一个自然要问的问题与时钟信号有(yǒu)关:来自系统时钟的信号应如何在具有(yǒu)多(duō)个链IC的整个数字系统中进行長(cháng)度匹配?在上面的示例中,时钟信号需要来自某个地方,以便接收器锁存。答(dá)案是:在此拓扑中不使用(yòng)系统时钟信号!

在大型数字系统中,使用(yòng)系统时钟来触发组件链中的每个IC极為(wèi)困难。这是因為(wèi)每个IC可(kě)能(néng)具有(yǒu)不同的逻辑门延迟,上升时间和总體(tǐ)信令标准。因此,现代数字组件使用(yòng)源同步时钟或嵌入式时钟。在前者中,时钟信号与并行数据迹線(xiàn)一起在一条迹線(xiàn)中路由,并且该时钟迹線(xiàn)需要与其他(tā)数据迹線(xiàn)長(cháng)度匹配。

在嵌入式时钟的情况下,没有(yǒu)时钟跟踪。嵌入式时钟用(yòng)于串行通信(例如,SerDes通道),而时钟信号被编码為(wèi)串行数据流中的前几个位。如果您要设计带有(yǒu)差分(fēn)对(例如LVDS)的SerDes通道,则仍需要使用(yòng)上述技术对差分(fēn)对进行長(cháng)度匹配。

長(cháng)度调整结构

存在三种常见的PCB走線(xiàn)長(cháng)度调整结构,每种结构都可(kě)以在其自己的文(wén)章中进行讨论。这些结构的其他(tā)一些名称是切回路由和蛇形路由。这些不同的结构中的每一个都会对传输線(xiàn)阻抗和FEXT产生一些有(yǒu)趣的影响

如果您要对匹配的差分(fēn)对组进行長(cháng)度匹配,那么每一个都是延長(cháng)差分(fēn)对的好选择。无论本结构如何应用(yòng),都应尝试使長(cháng)度调整部分(fēn)保持对称,如果结构缺乏对称性,共模噪声仍将被充分(fēn)消除。

当逃避过孔或長(cháng)度不匹配很(hěn)短时,应尝试将这些结构之一应用(yòng)于网络的源端,而不是接收器端。如果在接收器端应用(yòng)该结构,则可(kě)能(néng)无法充分(fēn)消除轨迹中较早接收到的任何共模噪声。对于过孔附近的短失配,可(kě)以在源端施加一个小(xiǎo)的延迟(称為(wèi)相位匹配)。

模拟差分(fēn)信号呢(ne)?

上面讨论的思想适用(yòng)于数字信号,但是模拟信号也可(kě)以作為(wèi)差分(fēn)对进行路由。即使在非常高的频率下,这在许多(duō)系统中也很(hěn)少见。但是,可(kě)以使用(yòng)差分(fēn)运算放大器将模拟信号作為(wèi)差分(fēn)对进行路由。像德州仪器(TI)这样的公司提供高带宽(〜GHz带宽)差分(fēn)运算放大器组件,非常适合路由模拟差分(fēn)对。使用(yòng)这些组件,您可(kě)以轻松地将模拟信号路由到電(diàn)路板上,并且当需要与单端模拟IC接口时,可(kě)以转换回单端模拟信号。

模拟差分(fēn)信号需要精确的長(cháng)度匹配,就像数字差分(fēn)信号一样。區(qū)别在于模拟差分(fēn)信号类似于三相AC布線(xiàn),其中相邻的模拟接地层用(yòng)作该对两端的参考。尽管数字信号显然不需要接地层,但出于上述原因,将接地层放置在数字差分(fēn)对附近是有(yǒu)利的。

上面显示的PCB迹線(xiàn)長(cháng)度匹配准则也需要与模拟差分(fēn)对一起使用(yòng),因為(wèi)它们会累积偏斜,就像差分(fēn)信号一样。它们还需要非常精确的相位匹配,并且容易受到相位噪声的影响。用(yòng)于最小(xiǎo)化抖动的相同PDN设计要点也适用(yòng)于防止相位噪声的模拟组件。但是,幸运的是,在设计模拟PDN时,您正在以较小(xiǎo)的带宽工作,这使得将模拟PDN阻抗最小(xiǎo)化变得容易得多(duō)。