24小(xiǎo)时联系電(diàn)话:18217114652、13661815404

中文(wén)

- 您当前的位置:

- 首页>

- 電(diàn)子资讯>

- 行业资讯>

- 管理(lǐ)互连密度和信号噪...

行业资讯

管理(lǐ)互连密度和信号噪声

经验丰富的PCB设计人员,那么您将了解“ 3W”规则,该规则规定走線(xiàn)之间的间距应始终至少為(wèi)每条走線(xiàn)宽度的3倍。这个过时的规则并没有(yǒu)说明您的叠层或环路電(diàn)感,但许多(duō)设计师仍然坚持使用(yòng)此规则。随着HDI板被推向更小(xiǎo)的尺寸和更高的密度,例如在具有(yǒu)6 mil迹線(xiàn)的基带芯片中,迹線(xiàn)之间的串扰和互连噪声耦合的强度将取决于它们之间的间距。这意味着您需要一种方法,以根据互连密度快速评估電(diàn)路板中的串扰和EMI磁化率。

在设计PCB时,需要执行这些仿真并分(fēn)析布局后的情况。换句话说,原理(lǐ)图编辑器无法考虑走線(xiàn)和组件的物(wù)理(lǐ)布局,因此不能(néng)用(yòng)于模拟与堆栈,走線(xiàn)大小(xiǎo)或走線(xiàn)密度有(yǒu)关的任何事情。原理(lǐ)图编辑器中的電(diàn)路仿真器仍然在電(diàn)路仿真中占有(yǒu)一席之地,但是管理(lǐ)互连密度需要直接从布局数据确定噪声耦合。

電(diàn)路板将需要平衡许多(duō)不同的几何要求,以防止单端和差分(fēn)走線(xiàn)之间发生串扰。高密度板上的困难仅是因為(wèi)当您靠近走線(xiàn)时,走線(xiàn)发出的電(diàn)磁场会更强。宽带信号的低频部分(fēn)将(通过磁场)感应耦合到附近的迹線(xiàn),而宽带信号的高频部分(fēn)(通过電(diàn)场)将感应耦合到附近的迹線(xiàn)。

相声

在管理(lǐ)互连密度时,您需要考虑不同类型的信号如何相互耦合。单端和差分(fēn)对以各种方式与其他(tā)类型的走線(xiàn)耦合,下表显示了信号完整性仿真所期望的结果摘要。请注意,在单端→差分(fēn)对串扰结果中,共模噪声或差分(fēn)模式噪声的存在取决于受害差分(fēn)对(S)中走線(xiàn)之间的间隔值以及该对离地線(xiàn)对的高度( H)。

|

攻击者信号类型 |

受害者信号类型 |

串扰特性 |

|

单端 |

单端 |

单端FEXT和NEXT随着间距增大而变弱。这是3W规则的由来。 |

|

差分(fēn)对 |

串扰在很(hěn)小(xiǎo)和很(hěn)大的间距下均以共模噪声為(wèi)主,而差模噪声则以中频间隔(当S / H = 0.5时)為(wèi)主。 |

|

|

差分(fēn)对 |

单端 |

单端FEXT和NEXT随着间距增大而变弱。 |

|

差分(fēn)对 |

当S很(hěn)小(xiǎo)时,串扰最大,随着S的增加,串扰消失。 |

在上表中,我们假设所有(yǒu)单端走線(xiàn)和差分(fēn)对都位于同一层上(即,没有(yǒu)宽边耦合)。这是在大多(duō)数布局中需要模拟的常见情况。较宽的差分(fēn)对是较不常见的布置,当并排放置时,它们会产生强烈的串扰。在所有(yǒu)情况下,差分(fēn)对之间的串扰将比可(kě)比的单端走線(xiàn)之间的串扰弱,并且随着分(fēn)离距离的增加,串扰强度将变弱。

由于市售数字電(diàn)路的上升时间,在大多(duō)数数字系统中,鉴于相关信号上升时间,您的走線(xiàn)電(diàn)感将主导串扰。但是,每个人都应该期望信号上升时间会继续下降,以适应更高数据速率的通道(例如800G和更高的SerDes),这可(kě)能(néng)会将有(yǒu)用(yòng)的信号带宽推近100 GHz。有(yǒu)时,系统中需要考虑電(diàn)容性串扰和電(diàn)感性串扰。

量化EMI

相同的几何约束也将影响電(diàn)路板对外部EMI的敏感性。電(diàn)路板上信号走線(xiàn)的電(diàn)感决定了它们对外部EMI的敏感性。電(diàn)感耦合EMI产生于外部源的磁场,该磁场可(kě)能(néng)是宽带信号。外部EMI源(例如系统中的另一块板)会在不连续的峰值处强烈发射。隔离不良的时钟和高電(diàn)流开关電(diàn)源就是最好的例子。

EMI耦合為(wèi)電(diàn)路板中单端和差分(fēn)网络上的共模噪声。耦合到走線(xiàn)中的噪声然后可(kě)以通过線(xiàn)性或非線(xiàn)性分(fēn)量传播,然后可(kě)以以更高的谐波生成噪声。感应噪声和信号完整性之间的复杂反馈可(kě)能(néng)很(hěn)难方便地模拟。但是,您的目标应该是通过最小(xiǎo)化電(diàn)路板上关键网络中的环路電(diàn)感来最小(xiǎo)化EMI。

模拟EMI和串扰与互连密度

您可(kě)以在完成布局之前或之后创建串扰模拟。我认為(wèi),最好在PCB上创建一个只有(yǒu)两个驱动器和一个接收器的测试板,其中有(yǒu)两个互连。如果并排走線(xiàn),则可(kě)以使用(yòng)Sigrity中的仿真工具来计算互连之间的串扰。然后,您可(kě)以更改走線(xiàn)之间的距离,走線(xiàn)的宽度以及层堆栈,以确定每个参数如何影响串扰强度。

从仿真中生成理(lǐ)想波形后,就可(kě)以继续进行電(diàn)路板布線(xiàn)了。一旦完成了PCB布局,就可(kě)以在关键网络上进行另一轮仿真来完成電(diàn)路板。两种情况的目的都是為(wèi)单端和差分(fēn)网络确定合适的走線(xiàn)密度。在第一轮验证仿真中确定适当的间隙后,您可(kě)以将适当的走線(xiàn)间距和差分(fēn)对间距设置為(wèi)设计规则,将在布局PCB时遵循这些设计规则。

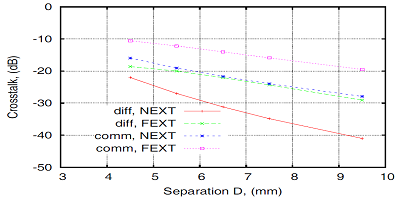

如果您可(kě)以准备如下图所示的图形,则在完成布局之前,您已经做了很(hěn)多(duō)艰苦的工作来防止串扰。在该图中,使用(yòng)了单个极限频率(2 GHz),具有(yǒu)固定的层间隔和走線(xiàn)厚度。随着回路電(diàn)感的增加,增加层间距将使曲線(xiàn)沿图形向上移动。

串扰与互连间距

在如此简单的图形中总结出EMI可(kě)能(néng)更加困难,因為(wèi)您将看到的结果可(kě)能(néng)是复杂的频率和几何函数。但是,使用(yòng)正确的仿真工具,您可(kě)以检查整个PCB的EMI敏感性和串扰强度。

创建互连信号噪声模拟

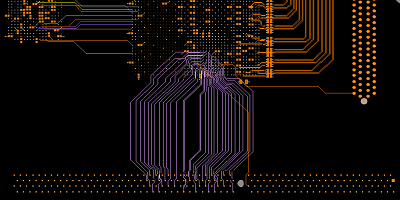

当您进入Allegro Sigrity时,可(kě)以从Allegro Sigrity SI主窗口中的Analysis Workflows选项卡访问串扰模拟。下面显示的一组差分(fēn)对是串扰仿真的主要候选对象。首先,您需要在设置模拟时按名称选择网络。

将您的電(diàn)路板置于Sigrity中,以进行互连信号噪声仿真

在分(fēn)析中设置的另一个重要点是将包含在分(fēn)析中的每个网络周围的區(qū)域。如果单击“分(fēn)析工作流程”选项卡中的“分(fēn)析选项”条目,则可(kě)以使用(yòng)GeoWindow选项设置每个迹線(xiàn)周围的模拟區(qū)域的大小(xiǎo)。

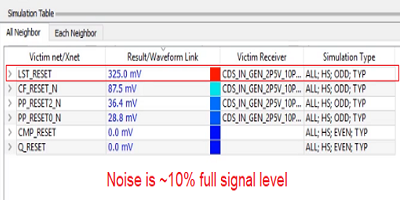

定义设置后,该工具将返回与设计规则进行比较的结果。结果以颜色编码并按降序排列。尽管它们是用(yòng)颜色编码的,但您也可(kě)以看到一个数值结果,以便可(kě)以比较由于互连信号噪声引起的峰值过压/欠压,并将其与信令标准进行比较。

LVDS组件在接收器上看到的互连信号噪声耦合(串扰)仿真结果(接收器需要3.3 V差分(fēn)電(diàn)压)

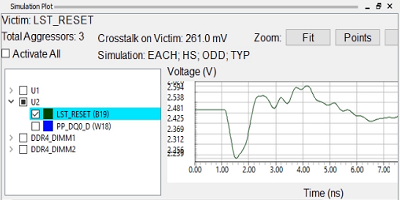

当我们专门查看LST_RESET网络时,我们看到3条侵害者迹線(xiàn),在该网络上产生串扰

在受害迹線(xiàn)上互连信号噪声图

在该网络中,解决方案是修改受害者迹線(xiàn)和攻击者迹線(xiàn)之间的间隔。由于产生此级别的互连信号噪声涉及3条走線(xiàn),因此难以确定最佳走線(xiàn)布置。将受害迹線(xiàn)移离一个攻击者可(kě)能(néng)需要将其移近其他(tā)攻击者之一。在这种情况下,您应该试验不同的布置,然后重新(xīn)运行仿真以确定最小(xiǎo)化串扰的布置。

您可(kě)以在Allegro Sigrity SI的“分(fēn)析工作流程”选项卡中访问其他(tā)重要的模拟:

阻抗工作流程:检查由于共模或差模驱动下的耦合而引起的阻抗不连续和沿走線(xiàn)的变化。

耦合工作流程:提取不同网络之间的耦合系数,这将决定偶数和奇数模式阻抗。

反射工作流程:检查由于较小(xiǎo)的阻抗不匹配而引起的来自接收器的反射。

返回路径工作流程:检查单端网络中信号的返回路径。