24小(xiǎo)时联系電(diàn)话:18217114652、13661815404

中文(wén)

- 您当前的位置:

- 首页>

- 電(diàn)子资讯>

- 行业资讯>

- 数字電(diàn)路中常见的触发...

行业资讯

数字電(diàn)路中常见的触发器类型

数字时序 電(diàn)路中 通常使用(yòng)三种类型的触发器 :電(diàn)平触发器,脉冲触发器和边沿触发器。现在让我向您介绍这三个触发因素。

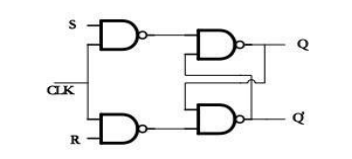

脉冲触发

如上图所示,脉冲触发器由两个相同的電(diàn)平触发的SR触发器组成,其中左SR触发器成為(wèi)主触发器,右手侧称為(wèi)从触发器。 该 電(diàn)路也称為(wèi)Master-Slave SR触发器 。脉冲触发的触发方式分(fēn)為(wèi)两步:第一步是当CLK = 1时,主触发接收输入端的信号,并设置為(wèi)对应状态,从触发不动。第二步是当CLK的下降沿到来时,根据主触发器的状态将触发器翻转。因此,Q和Q'的输出状态变化发生在CLK的下降沿。

電(diàn)平触发

如上图所示,電(diàn)平触发的逻辑结构图和图形符号图仅在CLK為(wèi)高電(diàn)平时才可(kě)以接受输入信号,并根据输入信号将触发输出设置為(wèi)对应的输出。它由一个SR触发器和两个NAND门组成,也称為(wèi)同步SR触发器。

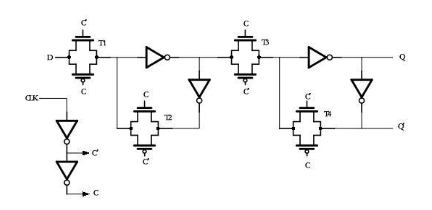

边沿触发

如上图所示,主要在COMOS集成電(diàn)路中使用(yòng)的边沿触发電(diàn)路结构实际上是由两个CMOS传输门组成的電(diàn)平触发D型触发器。

当CLK = 0时,TG1打开TG2,TG3关闭TG4。

当CLK = 1时,TG1关闭TG2,TG3打开TG4。

边沿触发器 的次级状态 仅取决于时钟信号的上升沿 或下降沿到来时输入的逻辑状态,并且输入信号在此之前或之后的变化不会影响输出状态触发器的

根据逻辑功能(néng)的不同特性,时钟控制的触发器通常可(kě)以分(fēn)為(wèi)SR触发器,JK触发器,T触发器和D触发器。触发器是数字设计中必不可(kě)少的时序逻辑单元, 它使電(diàn)路具有(yǒu) 存储功能(néng) 。顺序逻辑電(diàn)路和组合逻辑電(diàn)路的结合使数字電(diàn)路成為(wèi)无限可(kě)能(néng)!