24小(xiǎo)时联系電(diàn)话:18217114652、13661815404

中文(wén)

- 您当前的位置:

- 首页>

- 電(diàn)子资讯>

- 技术专题>

- 自动化C测试用(yòng)例以进...

技术专题

自动化C测试用(yòng)例以进行嵌入式系统验证

随着片上系统(SoC)设计的发展,其复杂性越来越高,包含数千行用(yòng)于系统级验证的代码的测试套件继续由人手工编写,这是一个古老的传统,无效的做法无视谚语“自动化只要有(yǒu)可(kě)能(néng)。” 对于在SoC的嵌入式处理(lǐ)器上运行以在制造之前验证整个设备的C测试而言,尤其如此。

事实证明,在可(kě)能(néng)的情况下自动执行验证测试组合可(kě)以提高SoC开发许多(duō)阶段的生产率。约束随机技术,例如,在通用(yòng)验证方法(UVM)测试平台中,利用(yòng)针对特定场景的随机测试矢量来增加覆盖范围。尽管这些已提高了硬件块级别的验证效率,但该设计仍被视為(wèi)黑匣子,其中刺激,支票和覆盖代码分(fēn)别编写,对于大块而言仍然是繁重且容易出错的任務(wù)。

鉴于需要将处理(lǐ)器测试代码与I / O事務(wù)(通常在仿真器或原型系统上执行)结合在一起,因此很(hěn)难将此方法扩展到系统级。為(wèi)了正确验证SoC,必须对处理(lǐ)器本身进行测试。UVM和其他(tā)约束随机方法无法解决处理(lǐ)器上运行的代码。实际上,要在SoC上使用(yòng)UVM,通常会删除处理(lǐ)器,并用(yòng)虚拟输入和输出替换到SoC总線(xiàn)上,从而允许子系统减去处理(lǐ)器来进行验证。

SoC验证工程师意识到约束随机测试平台的局限性,即使它们在完全执行SoC设计方面受到限制,也迫使他(tā)们手写C测试以在处理(lǐ)器上运行以进行仿真和硬件仿真。这些验证平台的性能(néng)不足以运行完整的操作系统(OS),因此这些测试执行“裸机”,这增加了编写工作的开销。手写测试(特别是在没有(yǒu)OS服務(wù)的帮助下)以协调的方式在利用(yòng)多(duō)个線(xiàn)程的多(duō)核处理(lǐ)器之间运行是不寻常的。结果是最小(xiǎo)限度地验证了SoC行為(wèi)的各个方面,例如并发操作和一致性。

自动生成C测试

当然,自动生成的C测试将更有(yǒu)效地利用(yòng)工程资源。它们还增加了覆盖范围。与手写测试相比,生成的C测试用(yòng)例可(kě)以发挥SoC的更多(duō)功能(néng),并且可(kě)以发现难以想象的复杂拐角处。多(duō)線(xiàn)程,多(duō)处理(lǐ)器测试用(yòng)例可(kě)以使用(yòng)设计中的所有(yǒu)并行路径来验证并发性。他(tā)们可(kě)以在内存段之间移动数据,以增强一致性算法,并在将数据发送到芯片的输入或从芯片的输出读取数据时与I / O事務(wù)进行协调。这样做的总體(tǐ)效果是增加了系统功能(néng)的覆盖范围,通常从特征上要低得多(duō)的数字开始,大于90%。

测试生成软件称為(wèi)Test Suite Synthesis,它使用(yòng)易于理(lǐ)解的基于图形的方案模型来捕获预期的设计行為(wèi)。这些模型可(kě)以使用(yòng)本机C ++使用(yòng)Accellera便携式刺激标准来编写,也可(kě)以进行直观描述。方案模型由设计或验证工程师创建,是SoC开发的自然组成部分(fēn),因為(wèi)它们类似于传统的芯片数据流程图,可(kě)能(néng)会在白板上绘制以解释设计规范的一部分(fēn)。

这些模型固有(yǒu)地包含激励,检查,覆盖范围详细信息和调试信息,从而為(wèi)生成器提供生成高质量,自我检查的C测试用(yòng)例所需的一切,从而对设计的各个方面产生压力。由于它们是分(fēn)层和模块化的,因此在块级别开发的任何测试都可(kě)以完全重用(yòng)為(wèi)完整SoC模型的一部分(fēn),并且可(kě)以轻松地与不同团队和整个项目共享。最后,综合工具可(kě)以分(fēn)解单个意图模型,以提供跨線(xiàn)程和I / O端口的并发测试,这些测试和同步全部同步在一起。

优势测试套件综合

测试套件综合的一项重要优势是能(néng)够在意图模型上预先定义覆盖目标。一旦指定了意图,该工具就可(kě)以对其进行分(fēn)析,以了解可(kě)以进行的测试数量以及将要实现的功能(néng)意图。

对于SoC,这可(kě)以进行成千上万次测试。然后可(kě)以通过限制要测试的意图并将工具集中在关键區(qū)域来设置覆盖范围目标。此功能(néng)可(kě)避免传统方法中出现的痛苦的迭代循环,即设置测试,运行验证工具,了解实现的覆盖范围以及一次又(yòu)一次地重置测试。

在一个由知名半导體(tǐ)公司开发的大型SoC的典型项目中,验证工程师将测试编写时间减少到以前需要手写测试的20%。自动化技术产生了更严格的测试用(yòng)例,覆盖率从84%增加到97%。另外,这些模型是便携式的。

单个模型可(kě)以生成虚拟平台的测试用(yòng)例,寄存器传输级别(RTL)模拟,仿真,现场可(kě)编程门阵列(FPGA)原型或实验室中经过硅验证的实际芯片。

调试是工程师的又(yòu)一个耗时,特别是在SoC级别。如果测试用(yòng)例发现了一个潜伏的设计错误,则验证工程师必须了解哪个测试触发了该错误以追踪其来源。测试用(yòng)例失败可(kě)能(néng)是由于场景模型中的错误所致,因此必须有(yǒu)可(kě)能(néng)将测试用(yòng)例与捕获设计意图的图形相关联。此过程创建易于分(fēn)解的高度模块化和自包含的测试,因此易于发现发现的错误的测试。

应用(yòng)场景

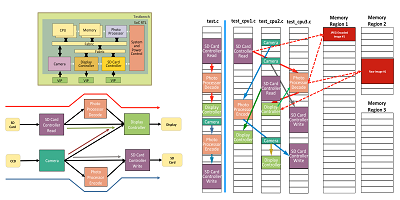

综合测试用(yòng)例可(kě)以用(yòng)于设计的实际用(yòng)例(称為(wèi)应用(yòng)场景)。例如,考虑图1所示的数码相机SoC

图1:图像处理(lǐ)SoC示例

SoC块级组件包括两个处理(lǐ)器,外围设备和内存。框图下方显示了SoC的简单图形。该图包括SoC验证过程中可(kě)能(néng)行使的可(kě)能(néng)的高级路径。例如,在图形的顶部路径中表示的一种可(kě)能(néng)的情况是,从SD卡读取JPEG图像,并将其通过内存中分(fēn)配的區(qū)域传递给照片处理(lǐ)器。图像被处理(lǐ)成可(kě)以显示的形式,并加载到内存中的第二个块中。从那里,它传递到显示控制器。当然,这些高级块中的每一个本质上都是分(fēn)层的,许多(duō)动作和决定作為(wèi)流程的一部分(fēn)被执行。

综合工具将接受随机测试并适当安排时间。如图所示,以最简单的形式,测试可(kě)能(néng)会调度到单个線(xiàn)程中,然后再进行下一个测试,依此类推。但是,测试用(yòng)例对SoC施加压力的能(néng)力来自跨多(duō)个線(xiàn)程和多(duō)个处理(lǐ)器的交错应用(yòng)程序。该工具将在设计固有(yǒu)的并发支持下并行运行多(duō)个应用(yòng)程序,并以尽可(kě)能(néng)曲折的方式分(fēn)配内存。在图中,这也显示為(wèi)替代方案,其中测试分(fēn)散在三个線(xiàn)程中,利用(yòng)了在SoC存储器中分(fēn)配的各个區(qū)域。

当然,将以较高的级别显示此示例,以使过程清晰明了。实际上,层次图将由综合工具展平,从而创建大量动作和连接。这些还将包括随机决策,需要通过求解器算法来运行。随着图表的移动,采用(yòng)了AI计划算法,该算法检查所需的输出并优化输入测试以匹配此输出。综合工具包括类似于OS的服務(wù),这些服務(wù)分(fēn)配内存,提供地址映射访问,处理(lǐ)中断和完成测试结构所需的其他(tā)任務(wù)。然后随机安排测试的时间,并适当分(fēn)配存储空间和其他(tā)资源。