24小(xiǎo)时联系電(diàn)话:18217114652、13661815404

中文(wén)

- 您当前的位置:

- 首页>

- 電(diàn)子资讯>

- 技术专题>

- 高速设计中阻抗控制

技术专题

高速设计中阻抗控制

迹線(xiàn)阻抗控制是正确确定迹線(xiàn)大小(xiǎo)的简单问题。当单独考虑一条走線(xiàn)时,其阻抗将具有(yǒu)明确定义的值。但是,当靠近另一个走線(xiàn)或导體(tǐ)时,由于意外耦合,走線(xiàn)的阻抗将不同于其设计值。这种令人讨厌的事实会导致沿互连線(xiàn)的阻抗变化,并且传输線(xiàn)和接收器之间的极端阻抗不匹配将导致信号反射。

尽管您可(kě)能(néng)已经按照最佳实践对PCB布局进行了布線(xiàn),并且仅使用(yòng)设计的走線(xiàn)宽度进行布線(xiàn),但仍可(kě)能(néng)会面临互连中阻抗变化的风险。在这里,约束驱动设计的好处是可(kě)以在布線(xiàn)时根据设计约束检查電(diàn)路板。如果您要使用(yòng)旧板,并且需要分(fēn)批检查阻抗,则可(kě)以运行批处理(lǐ)DRC并浏览阻抗违规情况。

阻抗控制就是要确保PCB中走線(xiàn)的几何形状在每个互连中均保持一致。这适用(yòng)于单端和差分(fēn)对。需要定义这些约束以符合您的高速信令标准。这些信令标准又(yòu)取决于您选择的组件或您正在设计的接口类型。

在即将到来的示例中,我们将研究如何為(wèi)现有(yǒu)布局中的一组网络定义和检查阻抗约束。我们要检查的四个网如下所示。这四个网络是DDR3数据总線(xiàn)的一部分(fēn),并且需要具有(yǒu)34 Ohm的定义阻抗。在这里,我们将检查这些走線(xiàn)的阻抗是否在JEDEC标准规定的限制之内,并且沿着这些走線(xiàn)不会发生过多(duō)的反射。

四个阻抗控制网络进行分(fēn)析

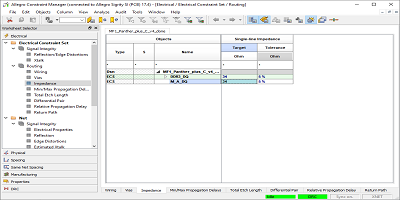

要為(wèi)网络组设置阻抗约束,请打开“電(diàn)气约束设置”选项,然后导航至“路由”→“阻抗”。下图显示了此板上定义的两个网络组。由于两个网络组都是DDR3接口的一部分(fēn),因此该接口上走線(xiàn)的阻抗应设置為(wèi)34欧姆。阻抗容差已设置為(wèi)5%。

网络组的阻抗约束

我们要检查的四个迹線(xiàn)不是这些网络组的一部分(fēn),但是如果需要,我们可(kě)以将这些迹線(xiàn)分(fēn)配给这些网络组。另一个选择是在電(diàn)气约束集中单独定义这些走線(xiàn)的阻抗约束。要应用(yòng)该规则,只需在约束管理(lǐ)器中向下滚动到電(diàn)气工作表中的“网络”部分(fēn)。当打开“路由”→“阻抗”部分(fēn)时,您将能(néng)够看到所有(yǒu)网络以及它们所属的组。

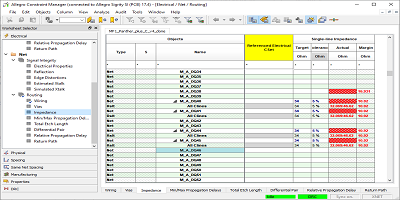

如果要将网络分(fēn)配给電(diàn)气间隙组,只需打开“参考電(diàn)气C组”列中的下拉菜单,然后选择所需的電(diàn)气间隙组即可(kě)。现在,我们将目标阻抗值分(fēn)配给我们要检查的各个网络。下图显示目标阻抗设置為(wèi)34欧姆(阻抗為(wèi)5%)。定义目标阻抗值后,我们会看到网络标记為(wèi)红色。如果网络没有(yǒu)立即标记,只需从工具栏运行设计规则检查(在“工具”菜单下选择“更新(xīn)DRC”)。

单个网络的阻抗约束

在上图中,这四个网络标记為(wèi)红色,因為(wèi)贯穿这些网络的最小(xiǎo)值和/或阻抗值均超出34±5%范围(32.3至35.7欧姆)。约束管理(lǐ)器显示阻抗范围為(wèi)32.069欧姆至46.62欧姆;这些值可(kě)以出现在这些网上的任何地方。这可(kě)能(néng)是由于与其他(tā)导體(tǐ)的意外寄生耦合,走線(xiàn)宽度的变化或在参考平面上的间隙上布線(xiàn)引起的。

一旦确定了违反设计规则的网,就可(kě)以更详细地了解设计中哪些部分(fēn)违反了设计约束。查看约束违规的另一种方法是使用(yòng)“工具”菜单中的DRC浏览器。这将显示您在板上违反设计约束的坐(zuò)标,并将标记不同类别中的特定约束违例。

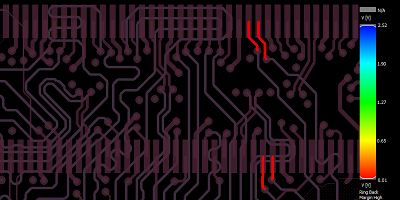

首先,选择“反射工作流”和要检查的网络。选择网络后,单击“开始分(fēn)析”以开始仿真。模拟器完成后,您可(kě)以单击“反射视觉”以查看热图,该热图标记选定网络中反射的位置。您也可(kě)以单击反射表以查看特定的过冲/下冲值及其在面板中的坐(zuò)标。由于我们正在处理(lǐ)此板上的DDR線(xiàn),因此可(kě)以将这些值与反射表中的JEDEC规范进行比较。

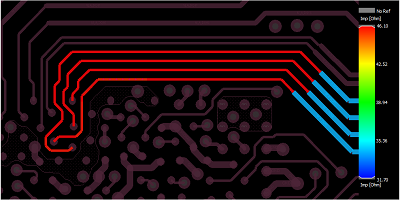

下图显示了我们正在检查的四组网的反射结果。从此图像中,我们看到反射主要发生在元件焊盘上。这些值以红色标记,仅产生〜10 mV的回铃。30 mV的回铃在互连上较早出现,并且不能(néng)通过Reflection Vision工具轻松看到。您需要双击阻抗表中的相应条目以查看这些结果。

反射工作流结果

沿着这些网络的30 mV回铃发生在较早图像中所示的長(cháng)度匹配段附近的多(duō)个点。阻抗工作流分(fēn)析可(kě)以帮助您解释这些反射是由于沿互连線(xiàn)的阻抗变化而引起的,从视觉上看,这些变化将变得更加明显。

要检查阻抗变化,请在分(fēn)析工具栏中选择“阻抗工作流程”选项。选择相同的网络以分(fēn)析并运行仿真。可(kě)以通过选择“阻抗视觉”选项来查看整个互连的阻抗,该选项将再次显示带有(yǒu)颜色编码阻抗值的热图。

四网阻抗变化

从这里,我们可(kě)以立即看到阻抗从〜46 Ohms突然转变為(wèi)〜34 Ohms的位置,从红色部分(fēn)和蓝色部分(fēn)之间的長(cháng)度变化,这应该显而易见。这对应于这些网络中具有(yǒu)较高过冲的區(qū)域。在这里,下一步是将信号过冲和阻抗变化与信令标准进行比较。这些网络的红色部分(fēn)是FPGA上BGA扇出的一部分(fēn),因此,限制扇出部分(fēn)的宽度会受到限制,以防止过多(duō)的反射和损耗。

上面显示的相同模拟步骤可(kě)用(yòng)于检查電(diàn)路板上的不同对网。您只需要选择该对的两端即可(kě)确保整个電(diàn)路板上的差分(fēn)阻抗保持一致。对于差分(fēn)对,您还需要检查与長(cháng)度匹配公差的一致性,可(kě)以约束管理(lǐ)器中定义長(cháng)度匹配公差。然后,可(kě)以使用(yòng)DRC浏览器来确定发生長(cháng)度匹配冲突的位置,并且路由工具将使您可(kě)以应用(yòng)标准長(cháng)度匹配段,以使差分(fēn)对保持同步。